# Design, Fabrication, and Characterization of Freestanding Mechanically Flexible Interconnects Using Curved Sacrificial Layer

Hyung Suk Yang, *Student Member, IEEE*, and Muhannad S. Bakir, *Member, IEEE*

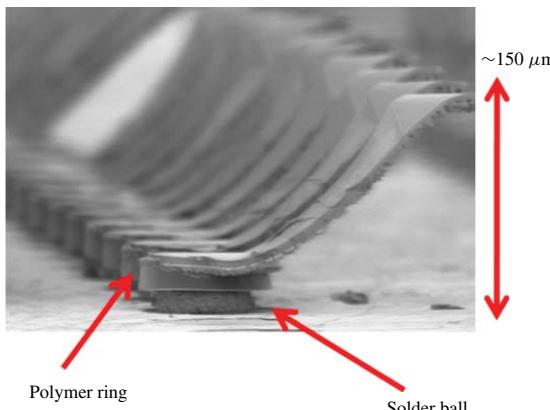

**Abstract**—Technologies that enable integration of microelectromechanical systems (MEMS) (and sensor) chip with a complementary metal-oxide semiconductor (CMOS) integrated circuit (IC) are becoming increasingly more important as the semiconductor industry explores and tries to encompass “More-than-Moore” solutions for future electronic systems. 3-D integration, stacking of dissimilar chips that have been independently fabricated and optimized, is a promising method to integrate MEMS and its signal processing electronics into a single miniaturized package. Unlike conventional methods of integration, 3-D integration can simultaneously provide high density and high performance interconnections without the added process complexity resulting from the CMOS and MEMS process reconciliation. Vital to the success of such integration are many novel interconnect technologies such as through-silicon vias, mechanically flexible interconnect (MFI) technology is another vital interconnect technology providing low stress, area array interconnections between a MEMS chip and a CMOS IC. MFIs are batch fabricated freestanding interconnect structures fabricated using two photolithography steps. The stand-off height of MFIs are 20  $\mu\text{m}$  and the dimension can be as small as 100  $\mu\text{m}$  by 50  $\mu\text{m}$ . In this paper, design, fabrication, and characterization of MFIs are presented, this paper also demonstrates SU-8 ring structures that allow fabrication and confinement of solder ball, so that MFIs can be assembled using a conventional flipchip bonder. Critical technology that enables fabrication of MFIs is the technology that uses reflowed photoresist as a sacrificial layer, development of such process is also discussed.

**Index Terms**—3-D integration, flexible interconnects, microelectromechanical systems/sensors integration, packaging.

## I. INTRODUCTION

WITH the advent of next generation electronics such as smartphones, patient-side health care systems and motion-enabled video gaming systems, integration of a microelectromechanical systems (MEMS) and sensors chip with a complementary metal-oxide semiconductor (CMOS) integrated circuit (IC) is becoming increasingly relevant and important. Of course, the need for such integration has always been in existence ever since the commercialization of

Manuscript received May 25, 2011; revised September 23, 2011; accepted October 18, 2011. Date of publication January 4, 2012; date of current version March 30, 2012. This work was supported in part by a Semiconductor Research Company GRC under Task 1825.001. Recommended for publication by Associate Editor E. D. Perfecto upon evaluation of reviewers' comments.

The authors are with the Georgia Institute of Technology, Atlanta, GA 30332 USA (e-mail: jyang@gatech.edu; muhannad.bakir@mirc.gatech.edu).

Color versions of one or more of the figures in this paper are available online at <http://ieeexplore.ieee.org>.

Digital Object Identifier 10.1109/TCPMT.2011.2177462

MEMS, and more generally, sensors. As a result, many different integration methods already exist for integrating CMOS and MEMS.

The conventional methods of integration can be broadly categorized as one of the two below [1]:

- 1) hybrid integration;

- 2) monolithic integration.

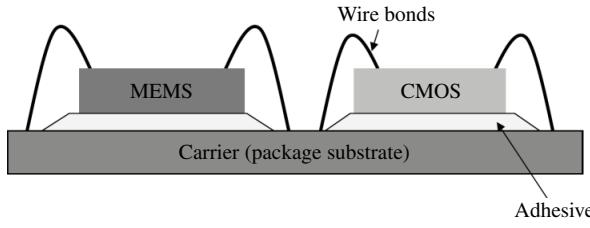

Hybrid integration (Fig. 1) refers to integration methods where MEMS devices are fabricated on one chip and CMOS electronics on another. Two dissimilar chips are then assembled onto a single package substrate and electrical connections are most commonly made using wirebonds. Flipchip bonding can also be used instead of wirebonds. When wirebonds are used, due to its non-batch fabrication method and peripheral array configuration, number of I/Os between MEMS and CMOS are often limited. Also, wirebonds' poor electrical performance can limit the performance of the entire system [2]. Even when flipchip bonding is used, the I/O density is limited by the minimum feature size of the package substrate and its performance limited by long and highly parasitic metal wires on the package substrate connecting two chips laterally.

Monolithic integration is an alternative to hybrid integration, where MEMS and CMOS are fabricated in the same silicon chip. Interconnections are made using on-chip metallization layers enabling high throughput and low latency communications. However, the CMOS process is often completed prior to the fabrication of MEMS devices and as a result, the type of processes and materials that can be used for the fabrication of MEMS devices are severely limited [3]. Also, the reconciliation of two already complex fabrication processes makes the realization a monolithic system costly.

Of course, for many of the applications, especially those with large manufacturing volumes, monolithic integration may prove to be the right solution. However, what is needed in the industry, and the reason why the package based integration is still the most popular method of integration, is that the cost and effort needed in making monolithic integration work is inaccessible to many developers, rather, a generic platform for integrating chips is needed.

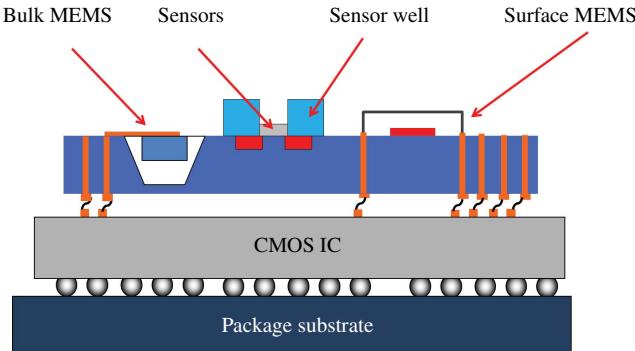

3-D integration on the other hand, has the potential to provide the best of both types of integration by stacking CMOS and MEMS chips on top of each other and making vertical electrical interconnection between them Fig. 2. With the 3-D integration, one can independently fabricate and optimize a CMOS IC and a MEMS chip then assemble and

Fig. 1. Hybrid integration of CMOS and MEMS.

Fig. 2. Using MFIs for 3-D integration of CMOS and MEMS.

interconnect them directly to each other using short and fine pitched vertical interconnects, this eliminates the need for process reconciliation as well as the need for routing signals through the package substrate.

However, having short and fine pitched wires are not the only requirement for the vertical interconnect technology if it is to be used for heterogeneous 3-D integration. First, the interconnect must be a CMOS compatible processes so that the presence of interconnects does not require altering of the fabrication process or change the performance of the CMOS devices on the chip. Second, the interconnect must not cause changes to the MEMS device performance or characteristics. More specifically, the interconnect must be able to isolate the MEMS chip from thermomechanical stress resulting from the CMOS ICs and package substrate's coefficient of thermal expansion mismatch, thermomechanical stress can cause the MEMS chip to warp which can affect sensitive MEMS devices. For example in one study, the performance of a MEMS device was changed as much as 37% as a result of the warpage [4].

## II. MECHANICALLY FLEXIBLE INTERCONNECTS (MFIs)

The concept of flexible structures as interconnects has been explored by other researchers before, beginning with multiple generations of works called sea-of-leads (SoL) [5]–[7]. SoL initially aimed to mitigate thermomechanical stress issues mainly by providing lateral compliance and lateral range-of-motion, and later work also included ways to provide few micrometers of stand-off height by using a sacrificial layer process. G-Helix [8], FlexConnect [9], [10] and  $\beta$ -Helix are other examples of continued works in this area. Other examples of compliant interconnects are discussed in [11].

However, with a continued discussion with the industry, it became clear that flexible interconnects can also be used

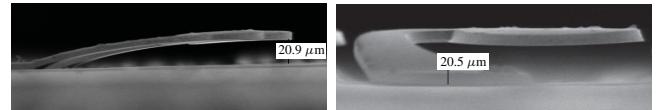

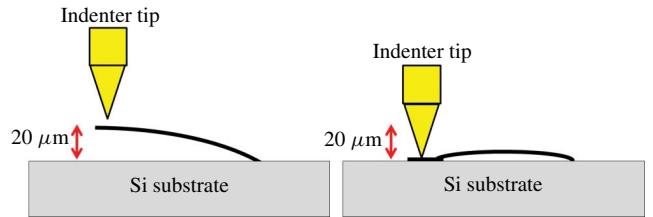

Fig. 3. Side views of MFIs.

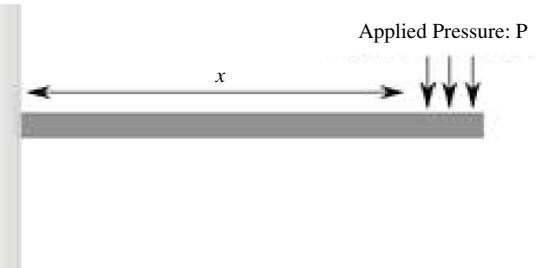

Fig. 4. Beam theory.

to address various other challenges and opportunities in the packaging field, aside from the stress relieving application, a flexible interconnect technology also has the potential to address following challenges and opportunities.

First, flexible interconnects can be used to compensate for non-planar surfaces that may exist, source of non-planarity could be on the substrate as well as from the inherent limitation of solder deposition method [12] or other bonding mechanisms.

Second, flexible interconnects can be used to make temporary interconnections enabling the idea of reusable electronics where the CMOS IC can be reused while the sensor chip is disposed. For areas where sensors are often irreversibly contaminated, or if the cleaning of the sensors does not make an economic sense, this ability to replace the sensor chip only can potentially bring down the cost of operation. An example of such area is the biosensor application, where sensors can be contaminated by blood or other bio-hazardous materials [13], [14]. It can also be used for interconnecting a macrochip with nanophotonics and proximity I/Os [15]–[18].

In both instances, one requires flexible interconnect structures to have a higher stand-off height and also a vertical range-of-motion that utilizes all of the available stand-off height. MFI technology is a wafer-level, two masking step process that can yield free standing copper structure with a stand-off height and vertical range of motion that extends up to 20  $\mu\text{m}$  [19], [20].

## III. DESIGN

Designing and optimizing the shape of the MFI is a critical part of the technology. MFIs have 20  $\mu\text{m}$  of vertical gap and in order to utilize all of 20  $\mu\text{m}$  of vertical gap, all aspects of the MFI shape had to be carefully engineered so that stress experienced by the beam structure is minimized and it is not constricted in any way during the deformation process.

### A. Constant Stress Design

From the Euler–Bernoulli classical beam theory, the bending stress of a symmetric rectangular beam at position  $x$  can be

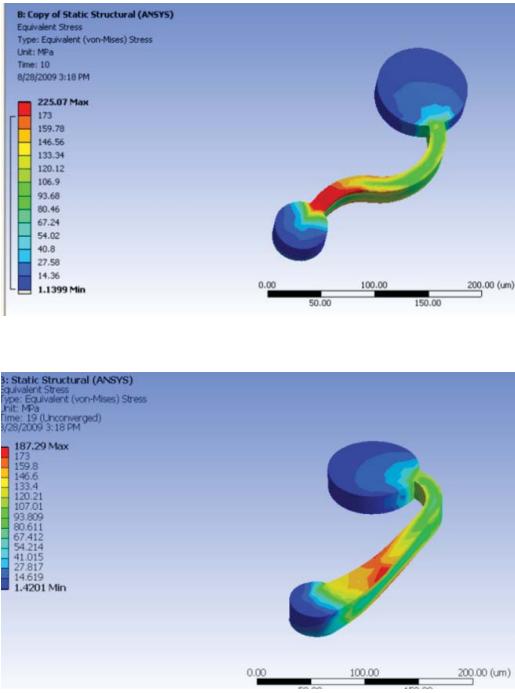

Fig. 5. ANSYS simulation showing that tapered design can be used to reduce the maximum stress experienced by the beam.

simplified and expressed as [21]

$$\alpha(x) = \frac{M(x) \cdot c}{I_x} \quad (1)$$

where,  $x$  is the distance from the fixed end,  $M(x)$  is the bending moment at distance  $x$ ,  $c$  is the distance from neutral axis to beam surface,  $I$  is the moment of inertial of beam cross-section.

For a cantilever with a single fixed point and pressure applied to the free end as shown in (Fig. 4), (1) simplifies to

$$\alpha(x) = \frac{6Px}{wt^2}. \quad (2)$$

Equation (2) shows that if the width of the beam is constant, stress will vary throughout the beam as a function of  $x$ , maximum stress is concentrated closed to the fixed end (when  $x = \text{length of the beam}$ ) and decreases toward the free end (when  $x = 0$ ). Constant width beam spreads the stress inefficiently.

However, if we vary the width of the beam linearly, (2) can be rewritten as following:

$$w = C_1 \cdot x \quad (3)$$

$$\alpha(x) = \frac{6P}{C_1^2} \quad (4)$$

$$= \text{constant}. \quad (5)$$

Stress is now constant throughout the length of the entire beam. Of course, similar results can be obtained by varying thickness of the beam, however, for a conventional photolithography processes, controlling the thickness of a structure is much more difficult than controlling the width.

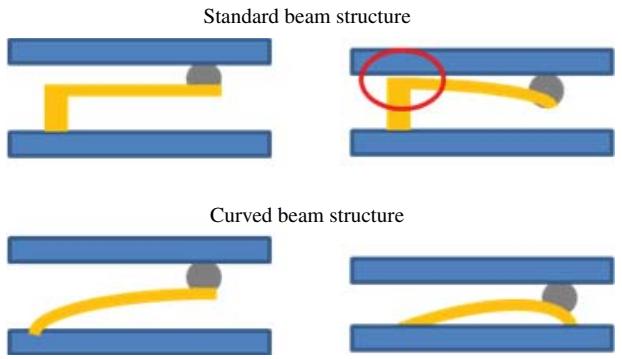

Fig. 6. Conventional cantilever structure constricts beam's vertical movement. Curved design has the potential to increase beam's range of movement significantly.

Using this concept, the width of the MFIs was also varied. It has the wider structure near the anchored point, and narrows toward the suspended pad area.

Two structures were modeled using ANSYS finite element method (FEM) and compared, one with a constant width and another with varied width design used by MFIs. The structures were modeled as an elastic material and constraints were applied identically to both structures. When the same vertical displacements were applied to both structures, the simulation showed that varied width structure of MFIs had a significantly lower maximum stress throughout the displacement as shown in Fig. 5.

This result is significant as the maximum stress experienced by the structure directly affects the vertical elastic range-of-motion MFIs can have. Elastic deformation is desirable as plastic deformation of the flexible interconnect structure can reduce reliability and in the worst-case scenario, cause instant catastrophic failure if the stress level is beyond the ultimate strength of the material. For temporary interconnect applications, elastic deformation ensures that MFI structures return to its original shape after every interfacing, and also increases the lifetime of the structures.

### B. Curved Design

In order to allow the 100% of the stand-off height to be utilized, it was also necessary to diverge from the conventional cantilever design as shown in Fig. 6. With the conventional beam, the range-of-motion would be restricted to the height of material deposited on the tip of the beam, which in this case was the height of the solder ball. By having a curved beam design as shown in Fig. 6, this problem can be avoided to some degree and it is the design used for the MFIs. Of course, creating such curved structure is not possible with the conventional lithography process. Next section describes fabrication processes for MFIs, including techniques to obtain the described curved beam structures.

### IV. FABRICATION PROCESS

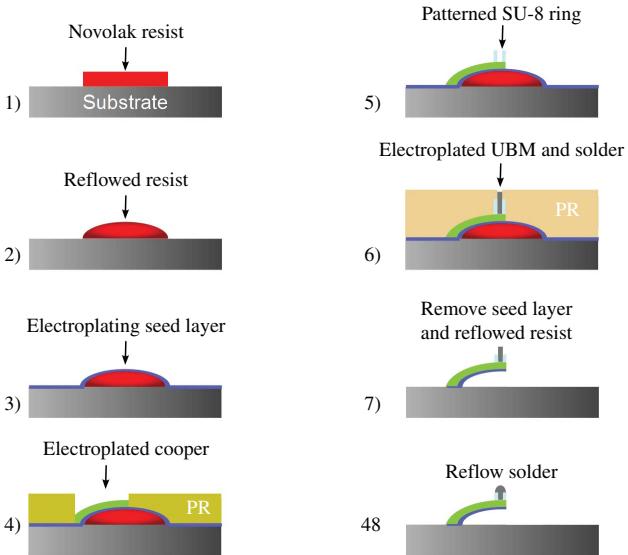

The fabrication process for MFIs is a two masking step process (Fig. 7). First, a sacrificial photoresist is defined using

Fig. 7. MFI fabrication process flow.

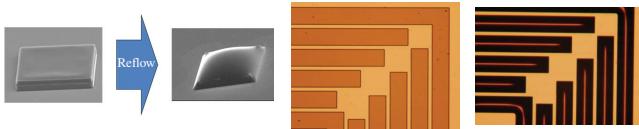

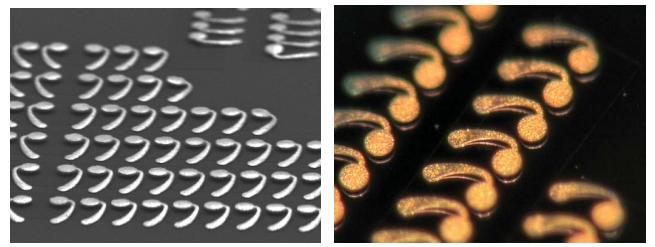

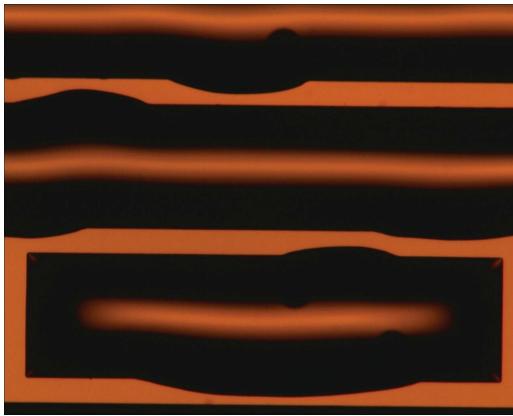

Fig. 8. SEM and microscope images showing the patterned photoresist before and after the reflow.

mask 1, and it is then reflowed and cured (Fig. 8). The total time for this process is less than 10 minutes.

Then, electroplating seed layers of Ti/Cu/Ti (30 nm/300 nm/30 nm) are deposited using a DC sputterer. A thick negative resist from Futurrex is then spin coated on top, then patterned using mask 2 to form a mold structure for electroplating.

After electroplating in an acidic copper sulfate bath, the electroplating mold is removed using acetone. Seed layer is then removed using buffered oxide etch and copper etchant. Finally, the reflowed photoresist removed using a resist removal solution leaving the freestanding MFI structure (Fig. 9).

#### A. Fabrication Challenges

1) *Electroplating Mold Exposure Control:* Patterning electroplating mold on top of a reflowed polymer was one of the first challenges that needed to be resolved. When a thick resist is spun on top form an electroplating mold, the resulting top surface of the resist was relatively flat when compared to the underlying reflowed polymer structure enabling a good contact lithography. However, the variation of the resist thickness due to this was as much as 20  $\mu\text{m}$  (the height of the reflowed photoresist layer). At first, the recommended exposure dose was used, however the thickest region of the MFIs were not completely cross-linked, causing undercutting during the development process. Undercutting of the electroplating mold caused electroplated structures as shown in Fig. 10.

On the other hand, when the exposure dose was increased, the resist on the curved region did not develop properly.

Fig. 9. Area array of MFIs.

Fig. 10. Result of electroplating using undercut mold.

Fig. 11. Reflowing at a constant high temperature resulted in shapes that deviated from the original patterned shape. Despite the same spacing in both of the lateral directions, the image on the right shows merging in only one direction. This indicates that the flow is laterally nonuniform and need to be minimized.

One likely cause of such result is that, the reflection of the light on the curved region of the dome resulted in inadvertent cross-linking of masked regions.

After experimenting with various thick negative resists, we have found a resist that was found to have a very wide sensitivity range and therefore suitable for this application. Exposure dose were experimentally determined and was found to be between the dose calculated for the thinnest part and the thickest part of the mold.

2) *Sacrificial Reflowed Photoresist:* Sacrificial reflowed photoresist (Novolac based) plays a critical role in fabricating MFIs—it is what enables the curved beam structure of MFIs, and at the same time, it allows 20  $\mu\text{m}$  of vertical gap to be realized using only two masking steps.

Though reflowed photoresist has been used frequently in the past for fabricating micro-lens structures, using it for sacrificial layer and at the dimension required by MFIs presented challenges not seen previously.

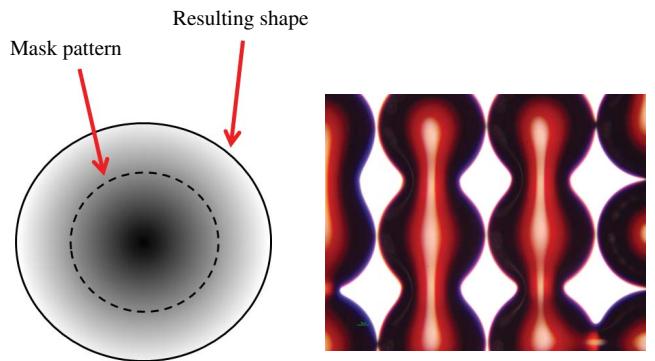

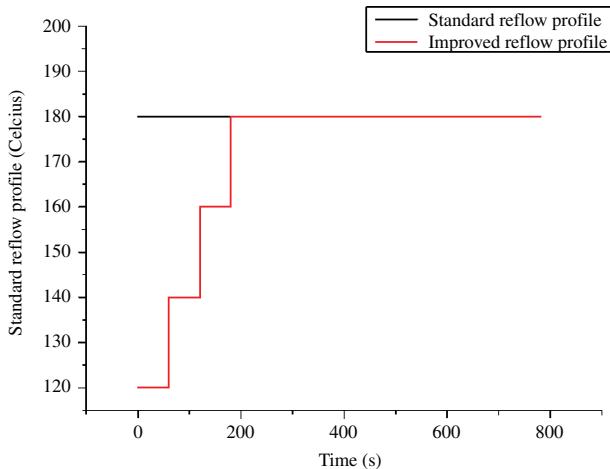

First challenge was determining the reflow and curing temperature profile. Initially, the reflow was performed using a

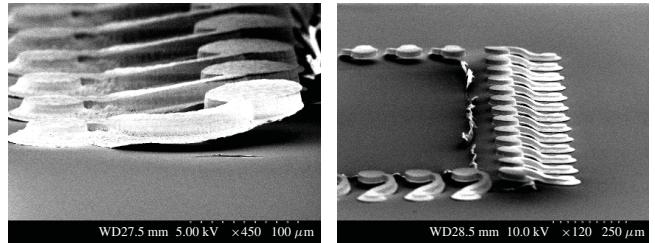

Fig. 12. Comparison of two reflow profiles. Left SEM shows polymer reflowed using the standard reflow profile. Right SEM shows improved reflow results using ramped reflow profile.

Fig. 13. Warpage of seed layer due to reflow of the photoresist after the deposition of seed layer.

hotplate at a constant temperature. During experimenting with the reflow process at various temperatures, two phenomena were observed. At lower temperatures still above glass transition temperature,  $T_g$ , the reflow of the photoresist was not complete. We suspect that this is due to the fact that  $T_g$  is raised above the temperature before the material had a chance to reflow completely. The result of partial reflow is a structure with local depletion and accumulation sites.

At higher temperatures the reflow was complete, however, the resulting structure was wider than the originally patterned structure. In extreme cases, photoresist merged with adjacent photoresist structures (Fig. 11). This is because as long as the photoresist is in the purely viscous state, the shape will continue spread to reach the equilibrium shape [22].

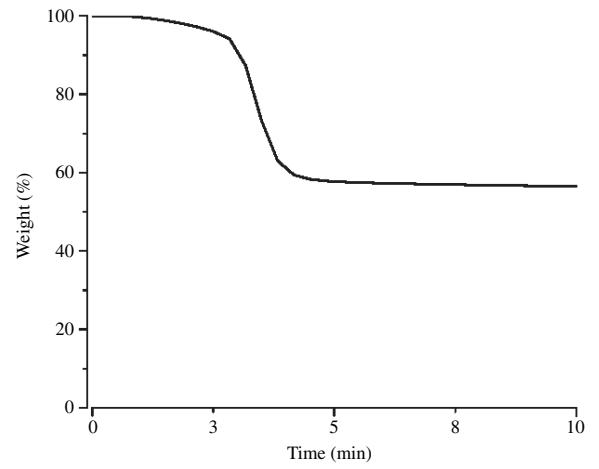

Fig. 14. Isothermal TGA performed at 180 °C.

Fig. 15. After curing the photoresist at 180 °C for 10 minutes, DSC results show that  $T_g$  has been raised above 150 °C.

Hence, what we need is a reflow temperature/profile that achieves complete reflow, while minimizing the spread.

The problem was resolved by using a ramped up reflow temperature profile. By ramping up the temperature, the photoresist underwent complete reflow and the expansion outside the original pattern was significantly reduced as shown in Fig. 12. We speculate that the new curing profile prevents the photoresist from going into fully molten state. It is well known that as Novolac based photoresist loses solvent content and crosslinked, the  $T_g$  increases [23], by incrementally increasing the temperature, the temperature is always only slightly above  $T_g$  putting the photoresist in partially molten state with high viscosity. Ramping up the temperature prolongs the period of this partially molten state, as the applied temperature is raised simultaneously as the  $T_g$  is raised.

The second challenge was in needing to do additional processing (notably, resist baking processes at 150 °C) on top of these reflowed photoresist. When the electroplating seed layer was deposited on top and electroplating mold spun coat, prebaked and post-baked, the outgassing from the reflowed photoresist caused a breakage in the seed layer. Even when the reflowed polymer was cured prior to the deposition of

Fig. 16. Depositing and confining solder in MFIs.

Fig. 17. SEM image of the assembled MFIs after the substrate has been pulled off. The solder is confined using the SU8 ring and remain confined even after assembly.

the seed layer, in some cases, the reflowed photoresist once again reflowed, causing visible warpage on the surface of the seed layer as shown in Fig. 13. Hence, it was important to systematically determine the curing parameters so that both the outgassing and reflow after the seed layer deposition are eliminated.

To determine the curing parameter required to eliminate outgassing, isothermal thermogravimetric analysis (TGA) was performed on the photoresist. The temperature was held at 180 °C, and the change in the weight of the photoresist was measured over time. The results show that less than 5 minutes of curing at 180 °C is required for the photoresist to reach a stable weight. Experimental results also show that curing duration of 5 min or longer at 180 °C was enough to eliminate breakage in seed layer due to outgassing, though the warpage caused by the reflow was still not eliminated. 180 °C was selected as the curing temperature as subsequent processing steps required 150 °C processes. By curing at 180 °C and verifying with TGA ensures minimal solvent evaporation and decomposing at this temperature or lower. The curing was performed at 180 °C instead of 150 °C in anticipating for hotplate temperature variation.

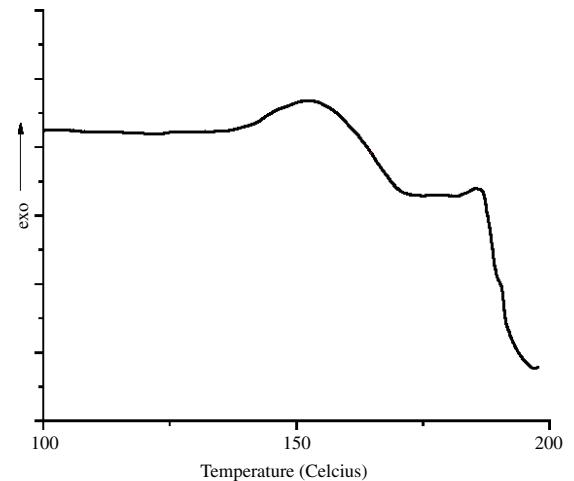

For eliminating the warpage, it was essential to raise the glass transition temperature of the photoresist to a temperature higher than the prebake and post-bake temperature. Using

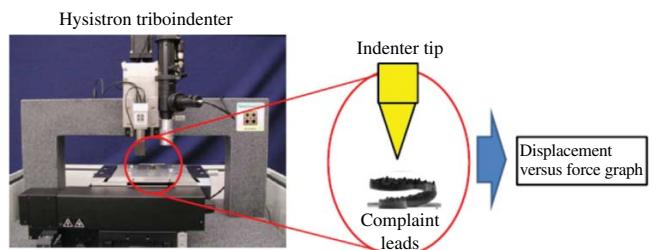

Fig. 18. Compliance testing setup using nanoindenter.

Fig. 19. Simulation and indentation results for MFI compliance.

differential scanning calorimetry (DSC), glass transition temperature of the photoresist after the cure process was determined. After curing the photoresist, the glass transition temperature was found to have been raised above the prebake temperature as shown in the Fig. 15. Experimental results also verify this result, after curing, the warpage on the seed layer from subsequent lithography process was completely eliminated. Similar results have been reported for Novolac-epoxy systems, which show DSC measuring increased Tg of a Novolac based resin to similar Tg after using the similar but isothermal curing process [24].

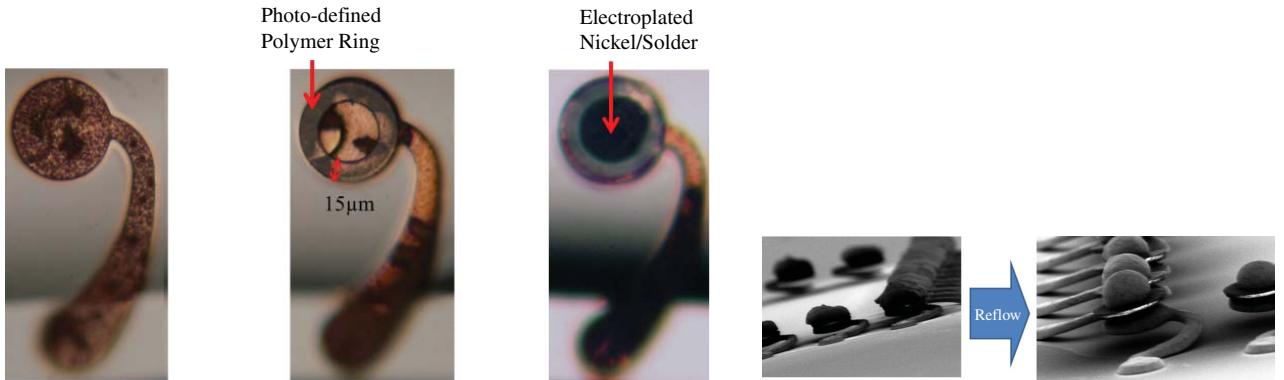

3) *Polymer Dome/Solder:* In order for MFIs to be used as permanent interconnects using solder balls, few additional steps are required. First, an SU-8 ring is formed around the

Fig. 20. Top graph shows the force and displacement graph of the first indentation and the bottom shows after 20th indentations of the same MFI. Linear and unchanged slope shows that minimal plastic deformation has occurred.

pad area, and nickel and solder are electroplated inside the ring, respectively. Electroplating mold for solder is processed the same way as the electroplating mold for the copper lead electroplating. The purpose of SU-8 ring is to confine the solder during the reflow stage and during the assembly when force is applied (Fig. 16).

For the assembly, 2 N of pressure was applied to the top chip with copper pads and the  $20 \mu\text{m}$  of vertical displacement of the interconnect structures were verified visually using a side view camera. After removing the top chip, it is possible to see that solder balls are completely confined to the pad area only even after pressure has been applied (Fig. 17).

## V. MECHANICAL SIMULATION AND CHARACTERIZATION

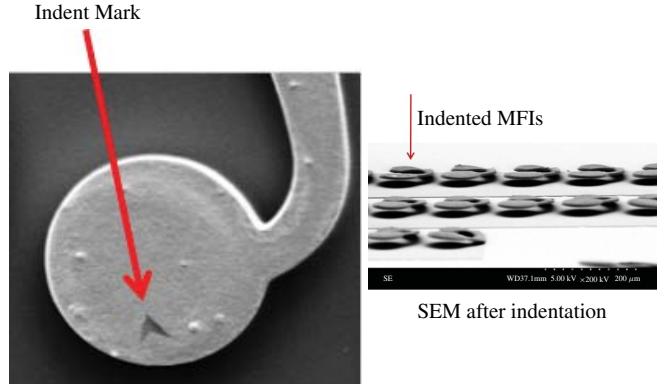

Compliance is an important metric for flexible interconnects as it determines the force applied to bonding pads during the assembly process. It is measured using a Hysitron Triboindenter, which has the capability to press on the pad area of the MFI and collect data for force versus displacement graph. From this graph, the slope is measured from the linear region which corresponds to compliance of the structure.

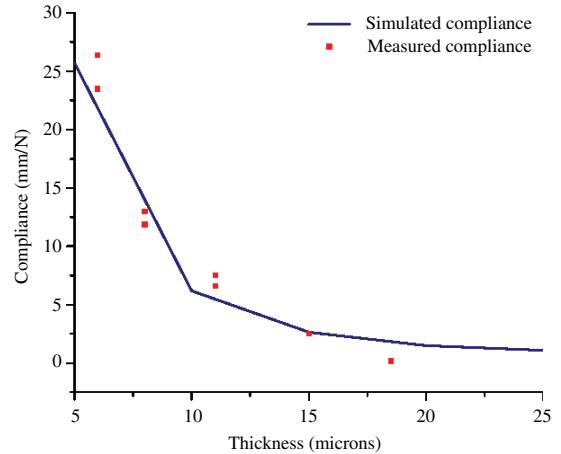

Compliance was measured for MFIs with varying thicknesses and compared to ANSYS FEM simulation results. Fig. 18 shows the experiment setup and Fig. 19 shows compliance determined by simulation and indentation.

It is important to note that a wide range of compliance can be obtained just by varying the thickness of the MFIs as a trivial process as only electroplating time needs to be changed. As a result, compliance of the MFIs can be tailored to meet the requirement of each application. For example, assembly on a low-k surface might require highly compliant MFIs while, using it as temporary interconnects require stiffer, relatively low compliant MFIs to apply enough force on the pad and make low resistance interconnections. The compliance requirement may also vary depending on the number and density of MFIs used in the application. For example, an

Fig. 21. Indentation using high force head flattens the pad area flat against the substrate.

Fig. 22. Even after the indenter presses the pad area flat against the substrate, the MFIs are returned to its original position as shown in the SEM (right).

inertial sensor may require a specific total compliance between the sensor chip and the CMOS chip, having the ability to change the compliance of individual MFIs allows one to reach this specific target without changing the number of MFIs used in the application, which may or may not be changed easily.

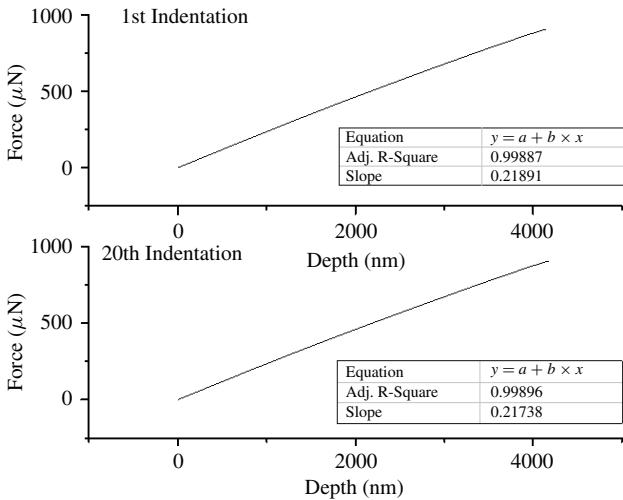

In order to determine the extent of plastic deformation, a single MFI was indented twenty times. Each time, the lead was vertically displaced by  $4.5 \mu\text{m}$  and its force versus displacement graph was measured. The results show that the first and the twentieth indentation results in linear curves with the difference between its slopes, within the margin of error of the equipment used. This result shows that the MFI underwent minimal if any, plastic deformation when deformed  $4.5 \mu\text{m}$  of vertically.  $4.5 \mu\text{m}$  was the vertical range limit of the equipment used for this experiment.

In another experiment, an indenter tip was used to press the MFI pad area flat against the substrate (Fig. 21), emulating the full deformation MFIs are expected to go through during some situations. The resulting structures were examined in an scanning electron microscope (SEM). SEM showed that the MFIs stand-off height remained  $20 \mu\text{m}$  even after the full deformation, again indicating minimal plastic deformation (Fig. 22).

## VI. CONCLUSION

In this paper, wafer level process for fabricating MFIs was described. The critical part of the process was the reflowed photoresist which was used as a sacrificial layer to create a free standing curved cantilever structure. Also by tapering the width of MFIs, it is possible to lower the maximum stress experienced by the beam and in conjunction with

the curved design, its range-of-movement is unrestricted and with minimal plastic deformation. The simulation result was verified experimentally with an indenter. Importance of curing the photoresist sacrificial layer was described and using DSC and TMA the process was optimized for improved process control and minimal processing time. MFIs mechanical properties were also simulated using a FEM software package and verified with measured data using nanoindenter. Also described is the wafer level process for depositing solder and confining it to the pad area only so that MFIs can be assembled using flipchip bonding tools.

#### ACKNOWLEDGMENT

The authors would like to thank M. Mutuza and M. Bolanos-Avila at Texas Instruments, Dallas, TX, and E. Luckowski at Freescale, Austin, TX.

#### REFERENCES

- [1] A. Witvrouw, "CMOS-MEMS integration: Why, how and what?," in *Proc. IEEE/ACM Int. Conf. Comput.-Aided Des.*, San Jose, CA: ACM, Nov. 2006, pp. 826–827.

- [2] A. J. Joseph, J. D. Gillis, M. Doherty, P. J. Lindgren, R. A. Previti-Kelly, R. M. Malladi, P. Wang, M. Erturk, H. Ding, E. G. Gebreselasie, M. J. McPartlin, and J. Dunn, "Through-silicon vias enable next-generation SiGe power amplifiers for wireless communications," *IBM J. Res. Dev.*, vol. 52, no. 6, pp. 635–648, 2008.

- [3] H. Baltes, O. Brand, G. K. Fedder, C. Hierold, J. G. Korvink, and O. Tabata, *CMOS-MEMS: Adv. Micro Nanosyst.*, vol. 2, New York: Wiley, May 2005, pp. 1–10.

- [4] M. Lishchynska, C. O'Mahony, O. Slattery, O. Wittler, and H. Walter, "Evaluation of packaging effect on MEMS performance: Simulation and experimental study," *IEEE Trans. Adv. Packag.*, vol. 30, no. 4, pp. 629–635, Nov. 2007.

- [5] M. Bakir, B. Dang, R. Emery, G. Vandentop, P. Kohl, and J. Meindl, "Sea of leads compliant I/O interconnect process integration for the ultimate enabling of chips with low-k interlayer dielectrics," *IEEE Trans. Adv. Packag.*, vol. 28, no. 3, pp. 488–494, Aug. 2005.

- [6] M. Bakir, H. Reed, H. Thacker, C. Patel, P. Kohl, K. Martin, and J. Meindl, "Sea of leads (SoL) ultrahigh density wafer-level chip input/output interconnections for gigascale integration (GSI)," *IEEE Trans. Electron Devices*, vol. 50, no. 10, pp. 2039–2048, Oct. 2003.

- [7] B. Dang, M. Bakir, C. Patel, H. Thacker, and J. Meindl, "Sea-of-leads MEMS I/O interconnects for low-k IC packaging," *Microelectromech. Syst. J.*, vol. 15, no. 3, pp. 523–530, Jun. 2006.

- [8] K. Kacker, G. C. Lo, and S. K. Sitaraman, "Low-K dielectric compatible wafer-level compliant chip-to-substrate interconnects," *IEEE Trans. Adv. Packag.*, vol. 31, no. 1, pp. 22–32, Feb. 2008.

- [9] K. Kacker and S. K. Sitaraman, "Design and fabrication of flexconnects: A cost-effective implementation of compliant chip-to-substrate interconnects," *IEEE Trans. Compon. Packag. Technol.*, vol. 31, no. 4, pp. 816–823, Dec. 2008.

- [10] K. Kacker and S. Sitaraman, "Electrical/Mechanical modeling, reliability assessment, and fabrication of FlexConnects: A MEMS-based compliant chip-to-substrate interconnect," *J. Microelectromech. Syst.*, vol. 18, no. 2, pp. 322–331, 2009.

- [11] M. S. Bakir and J. D. Meindl, *Integrated Interconnect Technologies for 3-D Nanoelectronic Systems*, 1st ed. London, U.K.: Artech House Publishers, Nov. 2008.

- [12] N. Basavanhally, D. Lopez, V. Aksyuk, D. Ramsey, E. Bower, R. Cirelli, E. Ferry, R. Frahm, J. Gates, F. Klemens, W. Lai, L. Yee, W. Mansfield, C. Pai, R. Papazian, F. Pardo, T. Sorsch, and P. Watson, "High-density solder bump interconnect for MEMS hybrid integration," *IEEE Trans. Adv. Packag.*, vol. 30, no. 4, pp. 622–628, Nov. 2007.

- [13] H. S. Yang, R. Ravindran, M. S. Bakir, and J. D. Meindl, "A 3D interconnect system for large biosensor array and CMOS signal-processing IC integration," in *Proc. IEEE Int. Interconnect Technol. Conf.*, Burlingame, CA, Jun. 2010, pp. 1–3.

- [14] R. Ravindran, J. Sadie, K. Scarberry, H. Yang, M. Bakir, J. McDonald, and J. Meindl, "Biochemical sensing with an arrayed silicon nanowire platform," in *Proc. 60th Electron. Compon. Technol. Conf.*, Atlanta, CA, Jun. 2010, pp. 1015–1020.

- [15] A. Krishnamoorthy, R. Ho, X. Zheng, H. Schwetman, J. Lexau, P. Koka, G. Li, I. Shubin, and J. Cunningham, "Computer systems based on silicon photonic interconnects," *IEEE Proc.*, vol. 97, no. 7, pp. 1337–1361, Jul. 2009.

- [16] I. Shubin, A. Chow, J. Cunningham, M. Giere, N. Nettleton, N. Pinckney, J. Shi, J. Simons, R. Hopkins, J. Mitchell, D. Douglas, E. M. Chow, D. DeBruyker, B. Cheng, and G. Anderson, "A package demonstration with solder free compliant flexible interconnects," in *Proc. 60th Electron. Compon. Technol. Conf.*, Las Vegas, NV, 2010, pp. 1429–1435.

- [17] I. Shubin, E. Chow, J. Cunningham, D. D. Bruyker, C. Chua, B. Cheng, J. Knights, K. Sahasrabuddhe, Y. Luo, A. Chow, J. Simons, A. Krishnamoorthy, R. Hopkins, R. Drost, R. Ho, D. Douglas, and J. Mitchell, "Novel packaging with rematable spring interconnect chips for MCM," in *Proc. 59th Electron. Compon. Technol. Conf.*, San Diego, CA, 2009, pp. 1053–1058.

- [18] X. Zheng, J. E. Cunningham, I. Shubin, J. Simons, M. Asghari, D. Feng, H. Lei, D. Zheng, H. Liang, C. Kung, J. Luff, T. Sze, D. Cohen, and A. V. Krishnamoorthy, "Optical proximity communication using reflective mirrors," *Lightw. Technol.*, vol. 23, no. 19, pp. 1800–1807, 2005.

- [19] H. S. Yang and M. S. Bakir, "3D integration of CMOS and MEMS using mechanically flexible interconnects (MFI) and through silicon vias (TSV)," in *Proc. 60th Electron. Compon. Technol. Conf.*, Las Vegas, NV, Jun. 2010, pp. 822–828.

- [20] H. S. Yang and M. S. Bakir, "Interconnect technologies for heterogeneous 3D integration: CMOS and MEMS," *MRS Proc.*, vol. 1249, no. 5, pp. 1249–1261, Apr. 2010.

- [21] J. M. Gere, *Mechanics of Materials*, B. J. Goodno, Ed., 7th ed. Toronto, ON: Cengage Learning, 2009.

- [22] H. Schift, C. Spreu, A. Schleunitz, and J. Lee, "Shape control of polymer reflow structures fabricated by nanoimprint lithography," *Microelectron. Eng.*, vol. 88, no. 1, pp. 87–92, Jan. 2011.

- [23] E. Fadda, "Bake mechanisms in novolak-based photoresist films: Investigation by contact angle measurements," in *Proc. SPIE*, Santa Clara, CA, 1996, pp. 460–468.

- [24] A. Hale, C. W. Macosko, and H. E. Bair, "Glass transition temperature as a function of conversion in thermosetting polymers," *Macromolecules*, vol. 24, no. 9, pp. 2610–2621, 1991.

**Hyung Suk Yang** (S'07) received the B.S. degree in computer engineering (high honor) and the M.S. degree in electrical and computer engineering from the Georgia Institute of Technology, Atlanta, in 2007 and 2008, respectively. He is currently pursuing the Ph.D. degree in electrical and computer engineering with the same university.

He has authored/co-authored 11 journal publications and conference proceedings. His current research interests include 3-D heterogeneous integration using novel microfabricated interconnect technologies.

Mr. Yang is a recipient of the Intel Ph.D. Fellowship in 2011. He won the SRC TECHCON Best in Session Paper Award in 2009 and 2010, the IMAPS Best Student Paper Award in 2009, and the IMAPS Best in Session Paper Award in 2009.

**Muhammed S. Bakir** (M'02) received the B.E.E. degree from Auburn University, Auburn, AL, in 1999, and the Ph.D. degree in electrical and computer engineering from the Georgia Institute of Technology (Georgia Tech), Atlanta, in 2003.

He is currently an Associate Professor with the School of Electrical and Computer Engineering, Georgia Tech. He is the editor of a book entitled *Integrated Interconnect Technologies for 3-D Nanoelectronic Systems* (Artech House, 2009).

Dr. Bakir has received 12 Best Paper Awards at the student/session/conference level with his colleagues. He is a member of the International Technology Roadmap for Semiconductors Technical Working Group for Assembly and Packaging. He was awarded the IEEE Components, Packaging and Manufacturing Technology Outstanding Young Engineer Award in 2011.